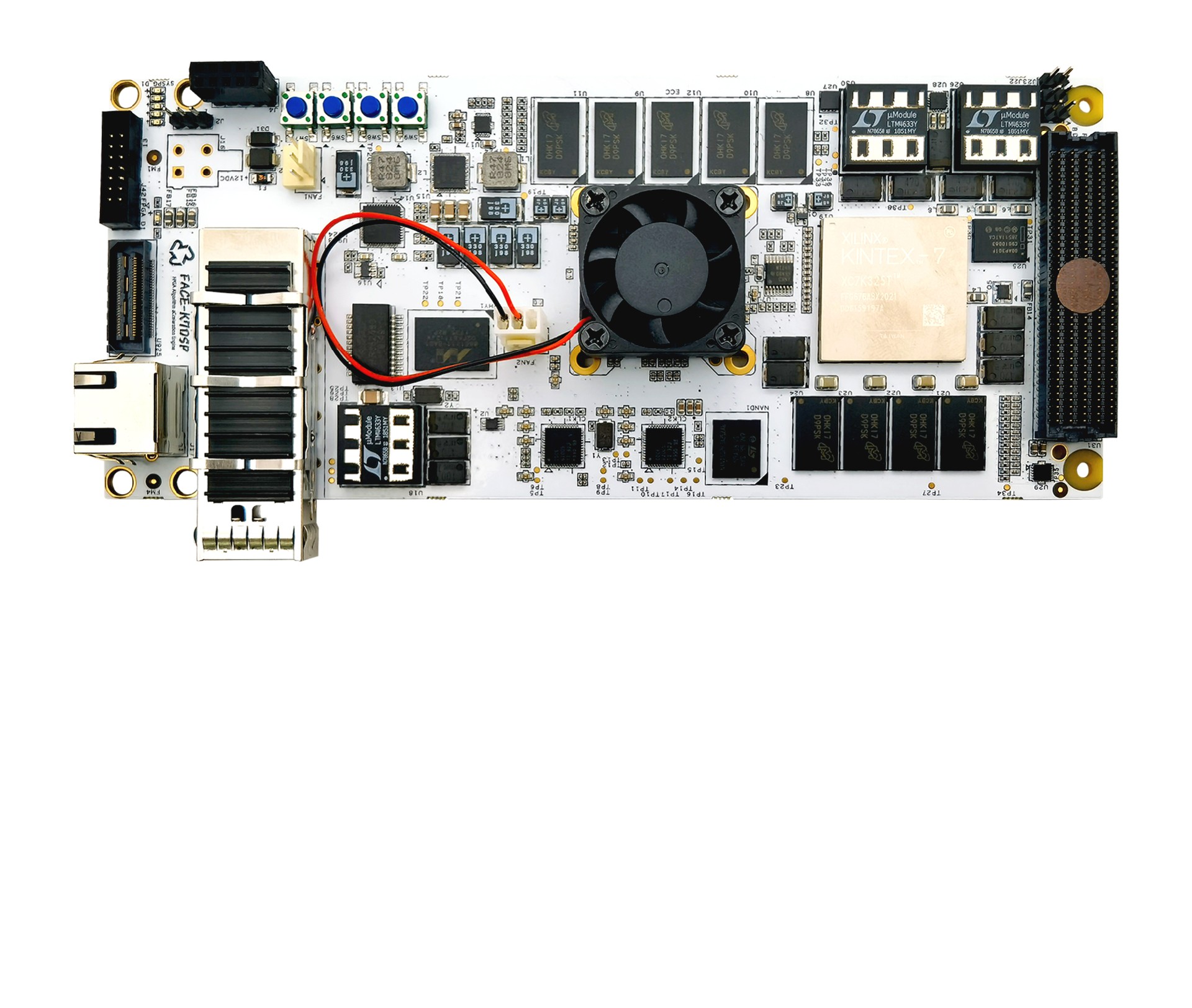

实物资源图如下:

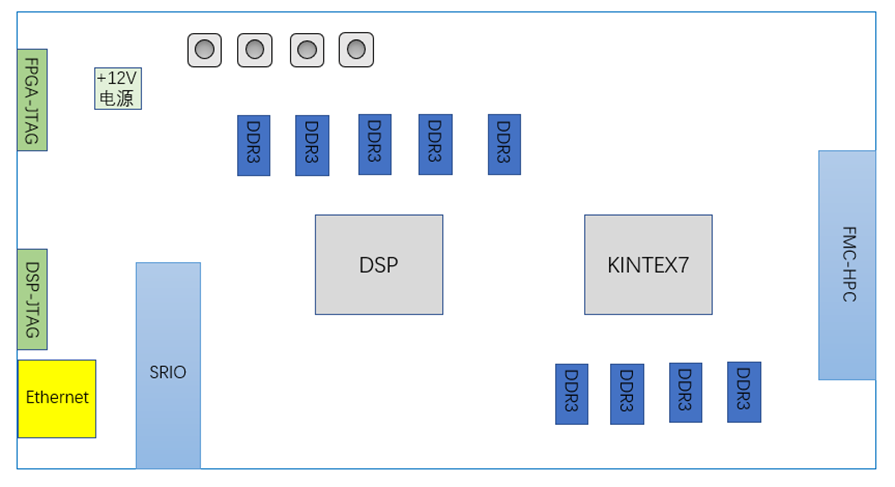

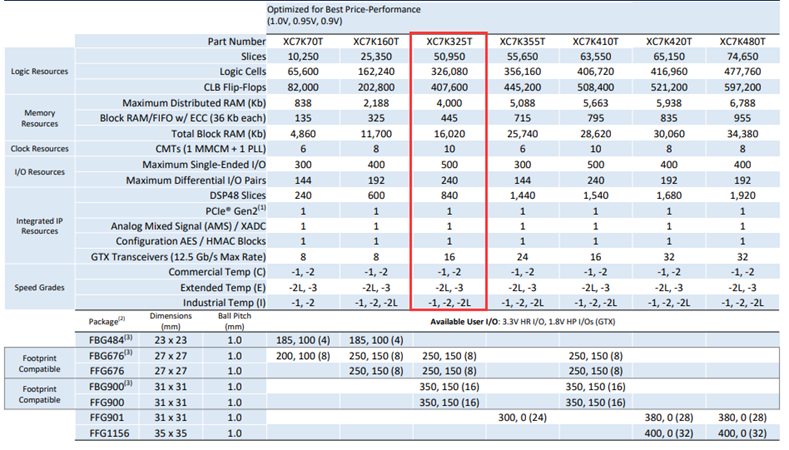

FACE-K7DSP硬件平台基于Xilinx Kintex7系列芯片(XC7K325T-2FBG676),其片上资源丰富。

逻辑资源326,080 Logic Cells

触发器数量407,600个

BRAM存储容量16,020Kb

DSP核心数量840个

高速串行收发器GTX(12.5Gb/s Max Rate)16个

用户可用IO数量500

通过SPI接口连接16MB SPI NOR FLASH,型号为N25Q128A11BSF40F;

通过IIC接口连接1Mbit EEPROM,型号为ST_M24M01-HRMN6TP,地址为0x50h/0x51h;

通过EMIF接口连接512Mbit NAND FLASH,型号为NAND512R3A2SZA6E。

名称 | 频率 | 时钟源 | 原理图标号 | 描述 |

DSP_PCIECLK | 100M | 6225 (CLK1) | DSP_PCIECLK_P | DSP部分PCIE参考时钟 |

DSP_PCIECLK_N | ||||

HyperLink_CLK | 312.5M | HyperLink_CLK_P | DSP部分HyperLink参考时钟 | |

HyperLink_CLK_N | ||||

SRIOSGMIICLK | 312.5 | SRIOSGMIICLK_P | DSP部分SRIO参考时钟 | |

SRIOSGMIICLK_N | ||||

REFCK | 100M | 6225 (CLK2) | REFCK_P | CLK1时钟源 |

REFCK_N | ||||

DDRCLK | 66.667M | DDRCLKP | DSP部分DDR4参考时钟源 | |

DDRCLKN | ||||

CORECLKP | 100M | CORECLKP | DSP系统时钟 | |

CORECLKN | ||||

PASSCLK | 100M | PASSCLKP | - | |

PASSCLKN |

SRIO测试

PCI Express测试

FPGA DDR3测试

其他开源参考案例

标准:主动散热

板载大功率电源 up to 100W

通用版型